1. Techniques for high performance low-power CMPs with Private L2 Caches- Chip Multiprocessors(CMPs) emerge as a dominant architectural alternative

- Most CMPs employ a large L2 cache to hide gap between the processor and off-chip memory

- Efficient L2 cache management is necessary

- High performance

- On-chip cache memory space is limited in CMPs

- Off-chip memory accesses require a much longer latency than on-chip communication costs

- Low power

- L2 cache becomes a major power consumer because of its size

- The leakage power consumption of the L2 cache becomes dominant in total power dissipation as the technology process advances below

2. Hybrid L2 cache organization

- Chip Multiprocessors(CMPs) emerge as a dominant architectural alternative

- Most CMPs employ a large L2 cache to hide gap between the processor and off-chip memory

- Efficient L2 cache management is necessary

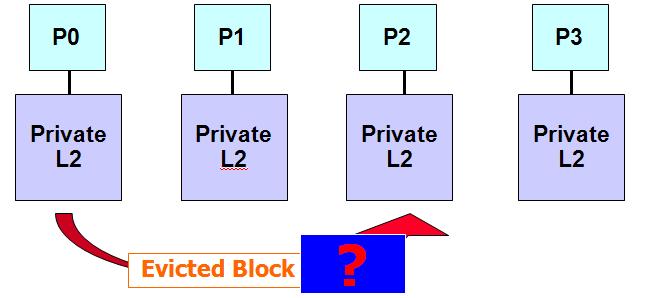

- Only when the evicted block is likely to be reused in the near future

- Only when writing the evicted block does not increase the leakage energy consumption

3. Published papers

Hyunhee Kim and Jihong Kim, "A Leakage-Aware L2 Cache Management Technique for Producer-Consumer Sharing in Low-Power Chip Multiprocessors," International Symposium on Low-Power and High-Speed Chips (COOL Chips XII), Yokohama, Japan, April 15-17, 2009

Hyunhee Kim, Jung Ho Ahn, and Jihong Kim, "Replication-Aware Leakage Management in Chip Multiprocessors with Private L2 Caches," International Symposium on Low Power Electronics and Design (ISLPED`10), Downtown Austin, Texas USA, August 18-20, 2010

Hyunhee Kim, Sungjun Youn, and Jihong Kim, "Reusability-Aware Cache Memory Sharing for Chip Multiprocessors with Private L2 Caches," Journal of Systems Architecture, Vol. 55, Issue 10-12, pp. 446-456, October 2009

Chun-Mok Chung and Jihong Kim, "Low-Power L2 Cache Design for Multi-Core Processors," IET Electronics Letters, Vol. 46, Issue 9, pp. 618-620, April 2010

Chun-Mok Chung and Jihong Kim, "Broadcast Filtering: Snoop Energy Reduction in Shared Bus-Based Low-Power MPSoCs ," Journal of Systems Architecture, Vol. 55, Issue 3, pp. 196-208, March 2009

Chun-Mok Chung and Jihong Kim, "L2 cache way prediction techniques for low-power MPSoC design," International Symposium on Low-Power and High-Speed Chips (COOL Chips XII), Yokohama, Japan, April 15-17, 2009

Hyunhee Kim and Jihong Kim, "A Leakage-Aware L2 Cache Management Technique for Producer-Consumer Sharing in Low-Power ," International Symposium on Low-Power and High-Speed Chips (COOL Chips XII), Yokohama, Japan, April 15-17, 2009

Hee-Joon Kang, Wonil Choi, and Jihong Kim, "A Leakage-Aware Shared L2 Cache Management Scheme for Low-Power Chip Multiprocessors," International Symposium on Low-Power and High-Speed Chips (COOL Chips XI), Yokohama, Japan, April 16-18, 2008

Chun-Mok Chung and Jihong Kim, "Broadcast Filtering-Aware Task Assignment Techniques for Low-Power MPSoCs," International Workshop on MEmory performance: DEaling with Applications, systems and architecture (MEDEA) held in conjunction with PACT 2007, Brasov, Romania, September. 16, 2007

Sungjune Youn, Hyunhee Kim, and Jihong Kim, "A Reusability-Aware Cache Memory Sharing Technique for High-Performance Low-Power CMPs ," International Symposium on Low Power Electronics and Design (ISLPED 2007), Portland, Oregon, August 27-29, 2007 (An earlier version of this paper was presented at the Workshop on Chip Multiprocessor Memory Systems and Interconnects (CMP-MSI)

Chun-Mok Chung, Jihong Kim, and Dohyung Kim, "Reducing Snoop-Energy in Shared Bus-Based MPSoCs by Filtering Useless Broadcasts," ACM Great Lakes Symposium on VLSI (GLSVLSI), Stresa-Lago Maggiore, Italy, March 11-13, 2007

강희준, 김현희, 김지홍, "캐시 파티션을 이용한 공유 2차 캐시 누설 에너지 관리 기법," 정보과학회논문지 : 시스템 및 이론 2010년 2월호, pp. 43-54

김현희, 김지홍, "임베디드 멀티프로세서 환경에서의 중복 데이터를 고려한 캐시 누전 에너지 관리 기법," 2009년도 대한임베디드공학회 추계학술대회 학술발표논문집, 2009.11

강희준, 김지홍, "누전 에너지 관리를 고려한 공유 캐시 파티션 정책," 대한전자공학회 소사이어티 추계학술대회, 제30권 제2호, pp. 759-760, 2007.11

정준목, 김진효, 김지홍, "MPSoC 플랫폼의 버스 에너지 절감을 위한 버스 분할 기법," 한국정보과학회, 논문지 : 시스템 및 이론, 33권 제9호 2006년 9월

정준목, 김진효, 김지홍, "MPSoC 플랫폼의 버스 에너지 절감을 위한 버스 분할 기법," 2006년도 컴퓨터시스템 학술대회 논문집, 2006년 6월

> Research Area > Multi-Proccesor System

> Research Area > Multi-Proccesor System